# Protokoll zum Praktikum des Moduls Technische Informatik an der JLU Gießen

Technische Informatik Versuch 2

Julian Bergmann, Dennis Getzkow 18. Juni 2013

## Versuch 2

## 1 Einführung

Im Versuch 2 sollte sich mit der Darstellung und Verarbeitung digitaler Werte (Wahrheitstabellen, boolische Operatoren), sowie mit Zahlendarstellungen und Addierer-/Subtrahierer-Bausteinen vertraut gemacht werden.

## 2 Vorbereitende Fragen

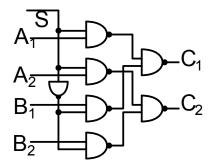

a) Aufgabe war das Zeichnen eines Schaltplan eines Multiplexers, der über einen Schalter entweder die 2-Bit-Eingänge A oder B weiterleitet unter Verwendung von 6 NAND und einem Inverter. Der Schaltplan hierzu ist in Abbildung 1.1 dargestellt.

Abbildung 1.1: 2-Bit Multiplexer mit Eingang für A, B und Schalter S

b) Die logischen Gleichungen für Ausgänge b, d und e einer Sieben-Segment-Anzeige (Siehe Aufgabenstellung für Wahrheitstabelle und Bezeichnung) lauten:

$$b = (\bar{A} \vee B \vee \bar{C} \vee D) \wedge (A \vee \bar{B} \vee \bar{C} \vee D) \wedge (\bar{A} \vee \bar{B} \vee C \vee \bar{D}) \wedge (A \vee B \vee \bar{C} \vee \bar{D}) \wedge (A \vee \bar{B} \vee \bar{C} \vee \bar{D}) \wedge (\bar{A} \vee \bar{B} \vee \bar{C} \vee \bar{D}) \wedge (\bar{A} \vee \bar{B} \vee \bar{C} \vee \bar{D})$$

$$d = (\bar{A} \vee B \vee C \vee D) \wedge (A \vee B \vee \bar{C} \vee D) \wedge (\bar{A} \vee \bar{B} \vee \bar{C} \vee D) \wedge (A \vee \bar{B} \vee C \vee \bar{D}) \wedge (\bar{A} \vee \bar{B} \vee \bar{C} \vee \bar{D})$$

$$e = (\bar{A} \vee B \vee C \vee D) \wedge (\bar{A} \vee \bar{B} \vee C \vee D) \wedge (A \vee B \vee \bar{C} \vee D) \wedge (\bar{A} \vee B \vee \bar{C} \vee D) \wedge (\bar{A} \vee B \vee \bar{C} \vee D) \wedge (\bar{A} \vee B \vee C \vee D)$$

$$\bar{C} \vee D) \wedge (\bar{A} \vee B \vee C \vee D)$$

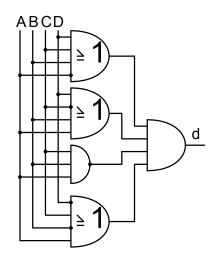

Die Gleichung für d wurde dabei so vereinfacht:

$$d = (\bar{A} \vee B \vee C \vee D) \wedge (A \vee B \vee \bar{C} \vee D) \wedge \overline{A \wedge B \wedge C} \wedge (A \vee \bar{B} \vee C \vee \bar{D})$$

oder in disjunktiver Normal

form:

$$d = (A \land B \land \bar{C}) \lor (A \land \bar{B} \land C) \lor (\bar{A} \land B \land C) \lor \overline{(A \lor C \lor D)} \lor (\bar{B} \land D)$$

Die Darstellung der konjunktiven Normalform ist in Abbildung 1.2 zu sehen.

Abbildung 1.2: Schaltung für d-Element von 7-Segmentanzeige

- c)  $+9_d = 1001_b$  entspricht 01001 im Zweierkomplemet.  $-9_d = 10111_b$  im Zweierkomplement.

- Zusätzlich zu den 4 Bits für die Wertedarstellung kommt das 5. als Vorzeichen hinzu.

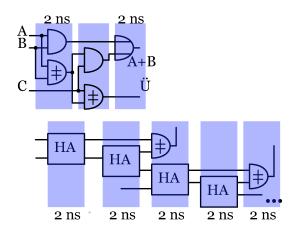

d) Zur Berechnung der Zeitdauer betrachten wir die Darstellung aus AND, OR und XOR. Hierbei stellen jeweils ein AND und XOR einen Halbaddierer dar und können parallel laufen. Dadurch ergibt sich für einen einzelnen Volladdierer mit 2 ns pro Gatter eine maximale Zeit von 6 ns.

Betrachten wir nun die Verkettung, stellen wir fest, dass der Übertrag des 2. Halbaddierers bereits nach 4 ns dem nächsten Volladdierer übergeben wird, dessen erster Halbaddierer also parallel zum OR-Gatter des Vorgängers läuft. Somit ergibt sich pro Volladdierer 4 ns plus 2 ns für das OR-Gatter des letzten Voll-Addierers:

$$t_{max,n} = n \cdot 4 \text{ ns} + 2 \text{ ns}$$

,  $t_{max,64} = 64 \cdot 4 \text{ ns} + 2 \text{ ns} = 258 \text{ ns}$

Zur Illustration der Denkweise ist die Abschätzung schematisch in Abbildung 1.3 dargestellt.

### Versuch

- 2. Nun sollte die in 1a skizzierte Schaltung aufgebaut werden. Hierzu siehe Abbildung 1.4

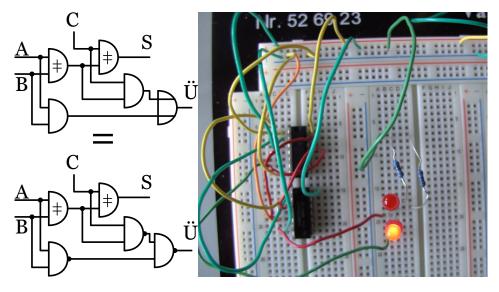

- 3. Über die De Morgan'schen Gesetze lassen sich OR und AND in einem 1–Bit–Volladierer über NAND–Gatter ausdrücken (Abbildung 1.5).

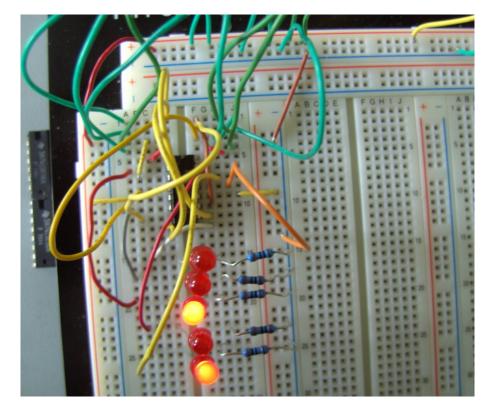

- 4. Benutzung des Addierer-Bausteins (7483): Hierbei wurden lediglich die Anschlüsse nach Anleitung an Eingänge bzw. LED angeschlossen (Abbildung 1.6).

- 5. Erweiterung des Addierers zu einem Subtrahierer mit Borrow. Hierzu wurden die 4 Bit der zweiten Zahl invertiert und 1 addiert, indem das Carry auf 1 gelegt wurde. Da das Ziel dieser Aufgabe in Aufgabe 7 verwendet wurde, siehe Abbildung 1.7.

Abbildung 1.3: Skizze zur Abschätzung der Aneinanderreichung mehrerer Volladdierer

Abbildung 1.4: Foto der aufgebauten und funktionierenden Schaltung des in 1a skizzierten Multiplexers

6. Hier sollte 4. und 5. über einen Schalter kombiniert und mit einer Sieben-Segment-Anzeige, wie in Abbildung 1.7 gezeigt, gekoppelt werden. Der Schalter wurde hierbei direkt mit dem Carry-Eingang des Addierers Verbunden, sodass bei S=1 = Subtraktion wie in 5. 1 addiert würde. Um die Invertierung der 2. Zahl nur bei S=1 durchzuführen, wurde das Invertierungs-Gatter mit einem XOR-Gatter ersetzt, welche jeweils als zweiten Eingang den Schalter erhalten. Statt der Dioden wurde nun das Ergebnis zu einem 7-Segment-Decoder und davon zu einer Sieben-Segment-Anzeige geleitet. Der Übertrag wurde weiterhin als LED sichtbar gemacht. In der Addition bedeutet der Übertrag ein Übersteigen des höchsten, anzeigbaren Wertes (Beispiel: 1111<sub>b</sub> + 0011<sub>b</sub> ergibt 10010<sub>b</sub>, also 0010<sub>b</sub> mit Ü=1). Bei der Subtraktion bedeutet das Überlauf-Signal, dass das Ergebnis negativ ist (hier wurde das erste Bit als Vorzeichen benutzt!) (Beispiel: 0010<sub>b</sub> − 0100<sub>b</sub> = 0010<sub>b</sub> + 1100<sub>b</sub> = 1110<sub>b</sub> = − (0001<sub>b</sub> + 1) = −(0010<sub>b</sub>) = −2<sub>d</sub>)

Abbildung 1.5: Skizze und Foto eines 1–Bit–Volladdierers aus 3 NAND– und 2 XOR–Gattern

Abbildung 1.6: Foto des Addierer–Bausteins 7483 mit Verkabelung zur Zahleneingabe und LED als Ausgaben–Visualisierung.

Abbildung 1.7: "'Taschenrechner"' kann mittels Schalter Addition und Subtraktion zweier 4–Bit Zahlen berechnen und gibt Überlauf als LED bzw. Ergebnis hexadezimal in einer Sieben–Segmentanzeige aus.